- 您现在的位置:买卖IC网 > Sheet目录1999 > IDT2309-1HPGGI (IDT, Integrated Device Technology Inc)IC CLK BUFFER ZD HI DRV 16-TSSOP

3

COMMERCIALANDINDUSTRIALTEMPERATURERANGES

IDT2309

3.3VZERODELAYCLOCKBUFFER

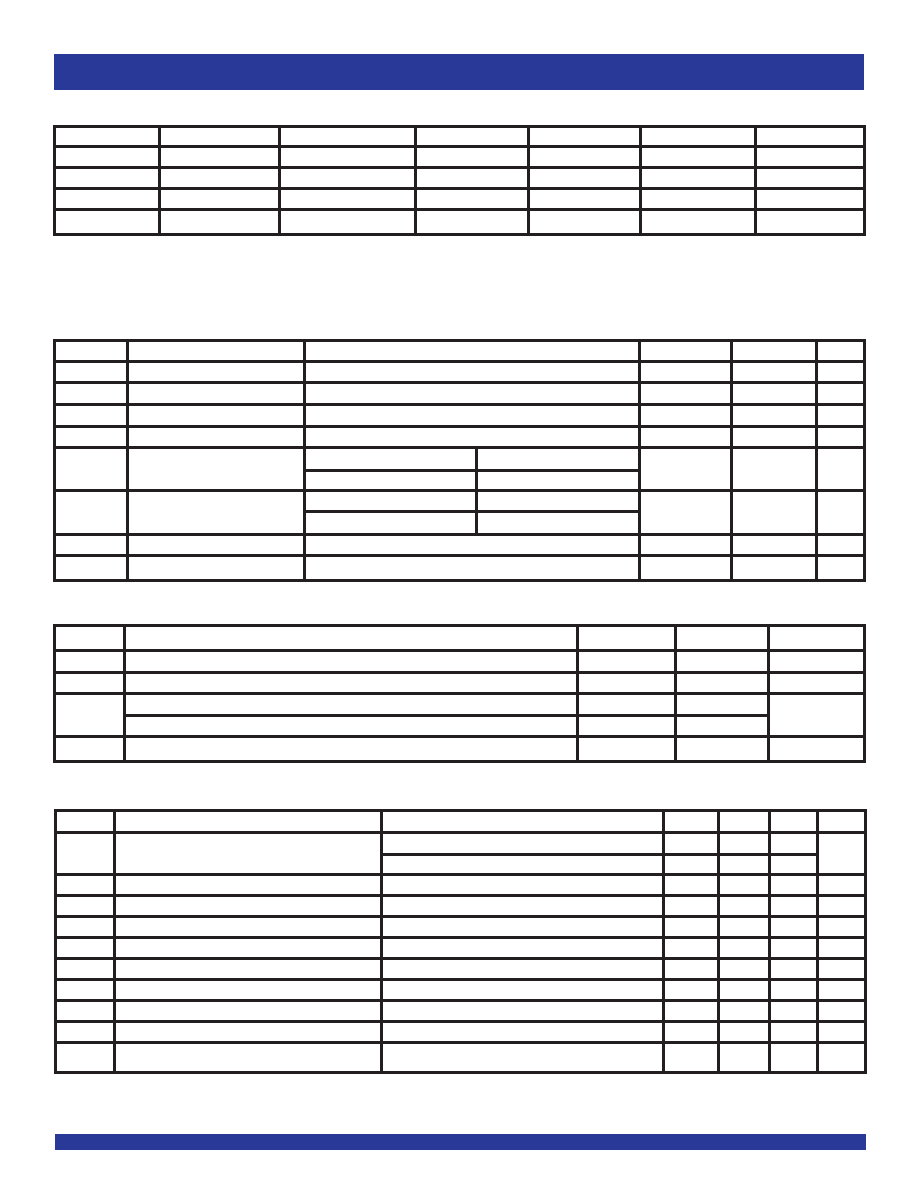

DC ELECTRICAL CHARACTERISTICS - COMMERCIAL

Symbol

Parameter

Conditions

Min.

Max.

Unit

VIL

InputLOWVoltageLevel

—

0.8

V

VIH

Input HIGH Voltage Level

2

—

V

IIL

InputLOWCurrent

VIN = 0V

—

50

A

IIH

Input HIGH Current

VIN = VDD

—

100

A

VOL

OutputLOWVoltage

StandardDrive

IOL = 8mA

—

0.4

V

High Drive

IOL = 12mA (-1H)

VOH

Output HIGH Voltage

StandardDrive

IOH = -8mA

2.4

—

V

High Drive

IOH = -12mA (-1H)

IDD_PD

Power Down Current

REF = 0MHz (S2 = S1 = H)

—

12

A

IDD

SupplyCurrent

Unloaded Outputs at 66.66MHz, SEL inputs at VDD or GND

—

32

mA

SWITCHING CHARACTERISTICS (2309-1) - COMMERCIAL

(1,2)

Symbol

Parameter

Conditions

Min.

Typ.

Max.

Unit

t1

OutputFrequency

10pFLoad

10

—

133

MHz

30pFLoad

10

—

100

Duty Cycle = t2

÷ t1

Measured at 1.4V, FOUT = 66.66MHz

40

50

60

%

t3

Rise Time

Measured between 0.8V and 2V

—

2.5

ns

t4

Fall Time

Measured between 0.8V and 2V

—

2.5

ns

t5

Output to Output Skew

Alloutputsequallyloaded

—

250

ps

t6A

Delay, REF Rising Edge to CLKOUT Rising Edge(2) Measured at VDD/2

—

0

±350

ps

t6B

Delay, REF Rising Edge to CLKOUT Rising Edge(2) Measured at VDD/2 in PLL bypass mode (IDT2309 only)

1

5

8.7

ns

t7

Device-to-Device Skew

Measured at VDD/2 on the CLKOUT pins of devices

—

0

700

ps

tJ

Cycle-to-Cycle Jitter

Measured at 66.66MHz, loaded outputs

—

200

ps

tLOCK

PLL Lock Time

Stable power supply, valid clock presented on REF pin

—

1

ms

NOTES:

1. REF Input has a threshold voltage of VDD/2.

2. All parameters specified with loaded outputs.

Symbol

Parameter

Min.

Max.

Unit

VDD

SupplyVoltage

3

3.6

V

TA

OperatingTemperature(AmbientTemperature)

0

70

°C

CL

Load Capacitance < 100MHz

—

30

pF

Load Capacitance 100MHz - 133MHz

—

10

CIN

InputCapacitance

—

7

pF

OPERATING CONDITIONS - COMMERCIAL

FUNCTION TABLE(1)

S2

S1

CLKA

CLKB

CLKOUT(2)

Output Source

PLL Shut Down

L

Tri-State

Driven

PLL

N

L

H

Driven

Tri-State

Driven

PLL

N

H

L

Driven

REF

Y

H

Driven

PLL

N

NOTES:

1. H = HIGH Voltage Level.

L = LOW Voltage Level

2. This output is driven and has an internal feedback for the PLL. The load on this ouput can be adjusted to change the skew between the REF and the output.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT2309A-1HPGG

IC CLK BUFFER ZD HI DRV 16-TSSOP

IDT2309B-1HPGGI

IC CLK BUFFER HIGH DRIVE 16TSSOP

IDT23S05-1HDCGI

IC CLK BUFFER PLL HI DRV 8-SOIC

IDT23S05E-1HDCGI8

IC CLK BUFFER PLL HI DRV 8-SOIC

IDT23S08-1HPGI8

IC CLK MULT PLL HI DRV 16-TSSOP

IDT23S08T-1DC

IC CLK MULT PLL ZD 2.5V 16-SOIC

IDT23S09T-1DC8

IC CLK BUFFER ZD 2.5V 16-SOIC

IDT5T929-30NLGI

IC CLOCK GENERATOR PREC 28VFQFPN

相关代理商/技术参数

IDT2309-1HPGGI8

功能描述:IC CLK BUFFER ZD HI DRV 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT2309-1HPGI

功能描述:IC CLK BUFF ZD PLL HIDRV 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

IDT2309-1HPGI8

功能描述:IC CLK BUFFER ZD HI DRV 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

IDT2309A

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:3.3V ZERO DELAY CLOCK BUFFER

IDT2309A-1DC

功能描述:IC CLK BUFFER ZD STD DRV 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

IDT2309A-1DC8

功能描述:IC CLK BUFFER ZD STD DRV 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

IDT2309A-1DCG

功能描述:IC CLK BUFFER ZD STD DRV 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT2309A-1DCG8

功能描述:IC CLK BUFFER ZD STD DRV 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)